Pressemitteilung

Dresden: Drei Fraunhofer-Institute haben in Dresden eine zukunftsweisende Forschungsinitiative gestartet: das Chiplet Center of Excellence (CCoE). Gemeinsam mit der Wirtschaft wollen sie die Einführung von Chiplet-Technologien vorantreiben. Dafür werden erstmals für die Automobilindustrie Workflows und Methoden für das Elektronik-Design, die Umsetzung von Demonstratoren sowie die Bewertung der Zuverlässigkeit entwickelt.

»Chiplets werden in den nächsten Jahren eine wichtige Rolle für die globale Halbleiterindustrie spielen. Denn diese Technologie bietet die größten Freiheitsgrade bei der passgenauen Gestaltung von elektronischen Systemen. Umso wichtiger ist es, dass die europäische Wirtschaft einen abgestimmten Fahrplan für die Entwicklung eigener Produkte und den Einsatz von Chiplets hat.« Davon ist Andy Heinig, Abteilungsleiter am Fraunhofer IIS/EAS und Leiter des Chiplet Centers of Excellence (CCoE), überzeugt. »Für Unternehmen ist es deshalb essentiell, frühzeitig die Umsetzbarkeit von Systemlösungen auf der Basis von Chiplets abschätzen zu können. Dafür haben wir am CCoE das breite Spektrum von Anforderungen und Randbedingungen an die Produkte im Blick und entwickeln daraus praxistaugliche Arbeitsabläufe und neue Verfahren zur Bewertung.«

Das CCoE verfolgt das Ziel, die Wettbewerbsfähigkeit und technologische Souveränität starker europäischer Industriesektoren zu unterstützen. In den ersten zwei Jahren wird sich das Center deshalb auf Anwendungen aus der Automobil-Elektronik konzentrieren. Hierfür werden verschiedene Schlüsselpartner entlang der Wertschöpfungskette zusammengebracht – vom Automobilhersteller bis zum Halbleiterproduzenten. Für sie wollen die Fraunhofer-Forschenden methodische Ansätze, Architekturkonzepte, nachnutzbare Basiskomponenten und Roadmaps für die Entwicklung, Fertigung und den robusten Aufbau von Chiplets erarbeiten. Darüber hinaus bewerten sie im Center verschiedene Chipletlösungen hinsichtlich ihrer Leistungsfähigkeit, Kosten und Zuverlässigkeit. Forschungsergebnisse sollen zudem in die internationale Normung einfließen und zur Gestaltung eines herstellerübergreifenden Chiplet-Ökosystems beitragen.

Die Alleinstellung des CCoE ergibt sich aus dem breiten Fraunhofer-Portfolio in der Elektronikentwicklung und -fertigung sowie der engen, interdisziplinären Zusammenarbeit mit der Industrie. Verantwortet wird das Center durch den Dresdner Institutsteil Entwicklung Adaptiver Systeme EAS, der zum Fraunhofer-Institut für Integrierte Schaltungen IIS gehört, durch das Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM und seinen Institutsteil All Silicon System Integration Dresden – ASSID sowie das Fraunhofer-Institut für Elektronische Nanosysteme ENAS. Interessierte Unternehmen, die sich an den vorwettbewerblichen Arbeiten des CCoE beteiligen und seine Forschungsagenda mitgestalten wollen, können dem Center bis Herbst 2024 beitreten. Weitere Informationen zum CCoE und zu Kontaktmöglichkeiten sind auf der folgenden Webseite zu finden: www.chiplet-center.fraunhofer.de.

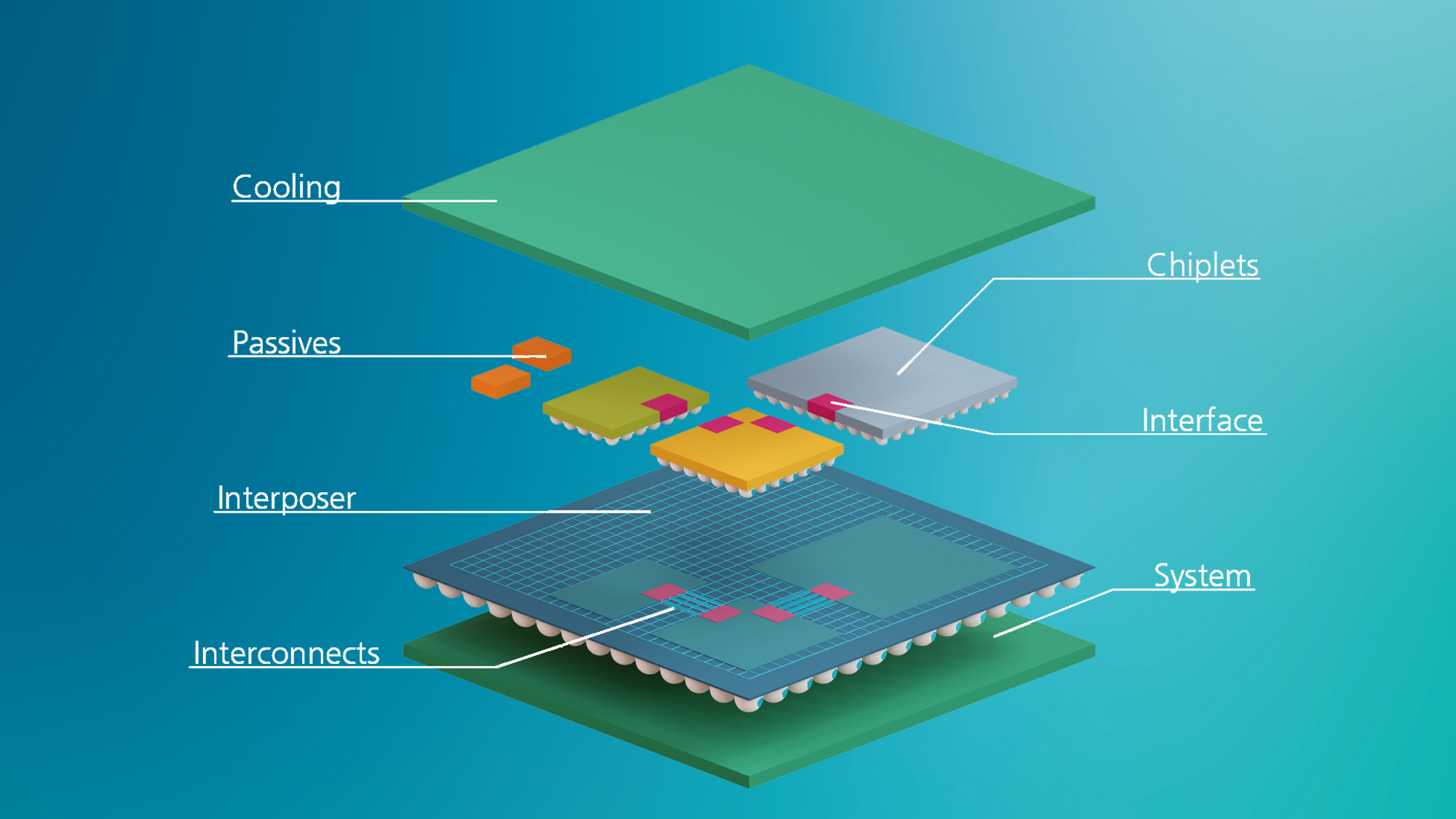

Hintergrund: Chiplets

Elektronik-Lösungen auf der Basis von Chiplets ermöglichen erstmals die Einbindung verschiedener Funktionseinheiten auch in unterschiedlichen Technologien auf einem Substrat oder in einem 3D-Chipaufbau. So erhalten Elektronik-Entwickler die Möglichkeit, die jeweils passfähigsten Fertigungstechnologien zu nutzen. Zum Beispiel können damit neueste und teure Technologien für bestimmte Funktionalitäten auf wenige Schaltkreise konzentriert werden, anstatt sie für den kompletten Chipaufbau verwenden zu müssen. Heute ist der Einsatz von Chiplets bereits für Anwendungen, die in Großserie produziert werden, wirtschaftlich und wird vor allem von US-amerikanischen Firmen im Bereich der Datacenter eingeführt. Allerdings werden dafür firmeneigene Standards genutzt. Eine Umsetzung mit Chiplets aus verschiedenen Quellen für Produktgruppen in kleineren und mittleren Stückzahlen, wie zum Beispiel für Automobil-Anwendungen, ist hiervon bisher weitgehend ausgenommen.

Über das Fraunhofer IIS/EAS

Das Fraunhofer-Institut für Integrierte Schaltungen IIS steht für internationale Spitzenforschung zu mikroelektronischen sowie informationstechnischen Systemlösungen. Die Wissenschaftlerinnen und Wissenschaftler am Institutsteil EAS in Dresden arbeiten daran, der stetigen Verkleinerung von Halbleiterbauelementen und der wachsenden Komplexität integrierter Schaltungen mit neuen Designkonzepten zu begegnen. Diese Expertise bringt der Institutsteil auch in die Arbeiten am CCoE ein. So werden anwendungsspezifische Entwurfsabläufe, neue Packaging-Konzepte für Chiplet-Lösungen, Teststrukturen oder angepasste Interface-IP entwickelt. Darüber hinaus ist die Gesamtleitung des Chiplet Centers of Excellence hier angesiedelt.

Über das Fraunhofer IZM

Das Fraunhofer IZM gehört seit über 30 Jahren zu den weltweit führenden Einrichtungen für angewandte Forschung und Entwicklung von robuster und zuverlässiger Elektronik und deren Systemintegration auf Wafer-, Chip- und Boardebene. Über 450 Mitarbeitende finden technologische Lösungen für zukünftige Herausforderungen wie das High-end Performance Packaging, die Quantensensorik, Hardwaresicherheit und Bioelektronik, nachhaltige 6G-Anwendungen oder Chiplets. Im Chiplet Center of Excellence wird das Fraunhofer IZM für die Realisierung von Demonstratoren verantwortlich sein und insbesondere seine Expertise für Aufbauten auf Waferlevel und Substraten einbringen. Hierfür stehen Prozesslinien für 200 und 300 mm 3D Waferlevel-Prozesse und eine 600 mm Substratlinie zur Verfügung.

Über das Fraunhofer ENAS

Das Fraunhofer ENAS ist Forschungs- und Entwicklungspartner im Bereich intelligenter Systeme für unterschiedlichste Anwendungen. In das CCoE bringt das Chemnitzer Institut seine langjährige Expertise im Bereich des Testens, der Zuverlässigkeitsbewertung sowie der Charakterisierung von Lösungen auf dem Gebiet der Elektronik- und Smart-Systems-Integration ein. Dabei wird das Fraunhofer ENAS Methoden für das virtuelle Testen und Prototyping von Chiplet-Komponenten und -Systemen entwickeln, mit denen sich die Funktionsfähigkeit und Zuverlässigkeit von Chiplet-Lösungen deutlich zeit- und ressourcenschonender optimieren lassen.

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme