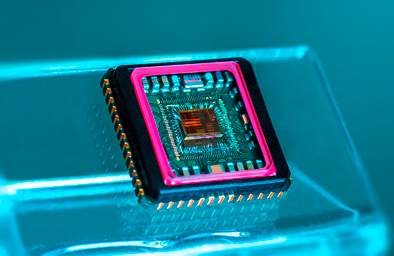

Mit steigendem Funktionsumfang elektronischer Systeme und zunehmender Miniaturisierung stoßen traditionelle Chipaufbauten immer stärker an ihre technologischen und wirtschaftlichen Grenzen. Durch neuartige Konzepte in der Systemintegration – wie die Chipstapelung oder der Einsatz von Interposern – kann ein höherer Datendurchsatz bei gleichzeitig sinkendem Energieverbrauch und reduziertem Flächenbedarf erzielt werden. Zudem ermöglichen moderne Packaging-Lösungen bis hin zu Chiplets die Einbindung unterschiedlichster Baugruppen wie Prozessoren, Sensoren und Funkschnittstellen in einem Baustein.

Besondere Herausforderungen beim Entwurf sind dabei die Beherrschung der Komplexität, die optimale Ausnutzung der zusätzlichen Freiheitsgrade und die Berücksichtigung der engen thermischen, mechanischen und elektrischen Kopplung im gestapelten System. Das Fraunhofer IIS/EAS unterstützt Sie bei der Lösung dieser Herausforderungen für ein optimales System-Packaging.

NEU: Zusammen mit dem Fraunhofer IZM und dem Fraunhofer ENAS haben wir eine zukunftsweisende Forschungsinitiative gestartet: das Chiplet Center of Excellence (CCoE). Gemeinsam mit der Wirtschaft wollen wir damit die Einführung von Chiplet-Technologien vorantreiben.

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS

Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS